Modul superkapasitorsering menghadapi masalah ketidakseimbangan tegangan antar sel.Yang disebut modul superkapasitor adalah modul yang berisi beberapa superkapasitor;karena parameter superkapasitor sulit untuk benar-benar konsisten, ketidakseimbangan tegangan rentan terjadi, dan beberapa superkapasitor mungkin mengalami tegangan lebih, yang secara serius mempengaruhi karakteristik keluaran dan masa pakai superkapasitor, dan bahkan menyebabkan kegagalan.

Dalam proses aplikasi superkapasitor, diperlukan penyeimbangan tegangan.Teknologi penyeimbangan tegangan yang ada terutama dibagi menjadi dua kategori: penyeimbangan pasif dan penyeimbangan aktif.

Keseimbangan Pasif

Penyeimbangan pasif adalah dengan menggunakan resistor dan sakelar atau dioda semikonduktor untuk menyeimbangkan tegangan, dan memainkan peran perlindungan tegangan lebih dengan mengonsumsi energi berlebih dari superkapasitor tegangan tinggi.Yang umum termasuk penyeimbangan resistor paralel, penyeimbangan resistor sakelar, dan penyeimbang tabung pengatur tegangan.

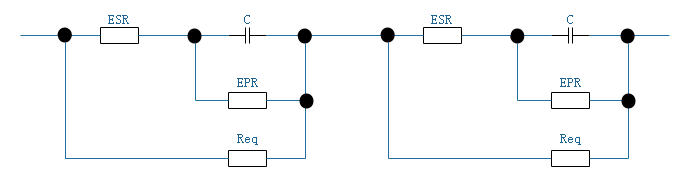

Di sini kita terutama berbicara tentang penyeimbangan tegangan resistor paralel paling sederhana (karakteristik dinamis tidak terlalu baik):

Req adalah resistor penyeimbang, yang terhubung langsung secara paralel dengan sel superkapasitor.Selama proses pengisian modul, sel juga mengeluarkan melalui Req, dan sel dengan tegangan tinggi keluar dengan cepat, sehingga memainkan peran perlindungan penyeimbang.Di sini, menurut metode pengisian yang berbeda (pengisian tegangan konstan dan pengisian arus konstan, keduanya dapat digunakan secara komprehensif dalam aplikasi praktis), ada juga perbedaan dalam kriteria untuk memilih Req.

Pengisian tegangan konstan

Dengan asumsi bahwa tegangan pengisian adalah U, karena tegangan modul superkapasitor dalam keadaan tunak pada dasarnya didistribusikan menurut EPR (kurang lebih rangkaian terbuka setelah C terisi penuh, dan ESR sangat kecil), setelah menambahkan Req, dapat sebenarnya dipahami sebagai mengganti EPR dengan Req, jadi Req harus memilih resistor dengan resistansi yang sama dan lebih kecil dari EPR, sehingga koneksi paralel dapat memainkan peran utama (umumnya 0,01~0,1EPR).Tegangan superkapasitor pada kondisi tunak adalah ReqU/(nReq).

Pengisian arus konstan

Dengan asumsi bahwa arus pengisian adalah I, setiap sel superkapasitor dan Req membentuk loop terpisah.Ketika tegangan sel kapasitor naik, arus yang mengalir melalui sel kapasitor turun, dan arus yang mengalir melalui Req meningkat.Ketika kapasitor terisi penuh, arus kapasitor adalah 0, dan tegangan sel kapasitor adalah ReqI, yaitu, ketika tegangan sel semua kapasitor seri mencapai ReqI, penyeimbangan selesai.Oleh karena itu, nilai resistor penyeimbang adalah Req=U(dinilai)/I.

Penyeimbangan Aktif

Penyeimbangan aktif adalah untuk mentransfer energi dari sel tegangan yang lebih tinggi atau seluruh modul ke sel lain sampai tegangan semua sel seimbang.Umumnya, kerugiannya relatif rendah, tetapi desainnya akan lebih rumit.Yang umum adalah penyeimbang konverter DC/DC, chip manajemen kapasitor super khusus, dll.

Kami adalahJYH HSU(JEC) Electronics Ltd (atau Dongguan Zhixu Electronic Co., Ltd.)yang memiliki lebih dari 30 tahun di industri komponen elektronik.Pabrik kami bersertifikat ISO 9000 dan ISO 14000.Jika Anda sedang mencari komponen elektronik, selamat datang untuk menghubungi kami.

Waktu posting: 17 Agustus-2022